# 2114 4096 Bit (1024x4) NMOS Static RAM

#### **FEATURES**

- · Cycle Time Equal to Access Time

- Completely Static No Clock Required

- Common Data Input and Output

- TTL Compatible Inputs and Outputs

- 883A Class B Processing Available

- Single + 5 Volt Power Supply

- Pin Compatible with industry standard 2114

- Maximum Access Time:

- ·200 ns (-2)

- -300 ns (-3)

- Maximum Power Dissipation:

- 370 mW (2114L)

- 525 mW (2114)

#### DESCRIPTION

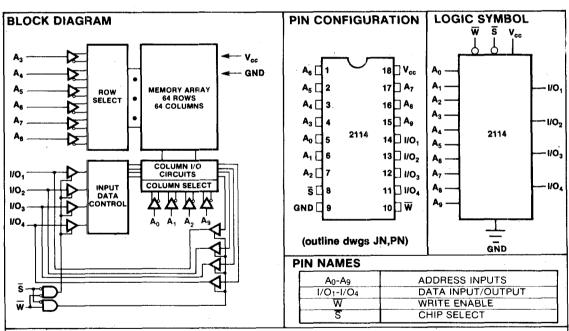

The 2114 is a 4096-bit static Random Access Memory organized 1024 words x 4 bits. The storage cells and decode and control circuitry are completely static, therefore no clocks or refresh operations are required. Memory access occurs within the specified access time after all address inputs are stable. A Chip Select input is provided for simple memory array expansion.

The 2114 is pin and performance compatible with the industry standard 2114 series, and the device is assembled in a standard 18-pin DIP for maximum system packing density.

#### ORDERING INFORMATION

| POWER |         |         |        |         |

|-------|---------|---------|--------|---------|

|       | 200ns   | 300ns   | 450ns  | PACKAGE |

| 370mW | D2114L2 | D2114L3 | D2114L | CERDIP  |

|       | P2114L2 | P2114L3 | P2114L | PLASTIC |

| 525mW | D2114-2 | D2114-3 | D2114  | CERDIP  |

|       | P2114-2 | P2114-3 | P2114  | PLASTIC |

8

#### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature 0°C t     | o +70°C  |

|---------------------------------|----------|

| Storage Temperature65°C to      | 5 +150°C |

| Voltage on Any Pin to Ground0.5 | V to +7V |

| Power Dissipation               | 1W       |

NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = +5V \pm 5\%$ ,  $T_A = 0$ °C to +70°C

|                        |                   |                                                      | 2     | 114L            | 2     | 114             |       |

|------------------------|-------------------|------------------------------------------------------|-------|-----------------|-------|-----------------|-------|

| PARAMETER              | SYMBOL            | TEST CONDITIONS                                      | MIN   | MAX             | MIN   | MAX             | UNITS |

| Input Load Current     | I <sub>INLD</sub> | V <sub>IN</sub> = 0V to 5.25V                        |       | 10              |       | 10              |       |

| Output Leakage Current | I <sub>OLK</sub>  | S = 2.4V,                                            |       | 10              |       | 10              | μΑ    |

|                        | Ì                 | $V_{I/O} = 0.4V \text{ to } V_{CC}$                  |       |                 |       |                 | -     |

| Power Supply Current   | I <sub>CC2</sub>  | V <sub>IN</sub> = 5.25V                              |       | 65              |       | 90              |       |

|                        |                   | $I_{I/O} = 0 \text{mA}, T_A = + 25 ^{\circ}\text{C}$ | 1     |                 |       |                 |       |

| Power Supply Current   | I <sub>CC1</sub>  | $V_{IN} = +5.25V$                                    |       | 70              |       | 100             | mA    |

|                        |                   | $I_{i/O} = 0$ mA, $T_A = 0$ °C                       | 1     | 1               |       |                 |       |

| Input Low Voltage      | V <sub>IL</sub>   |                                                      | - 0.5 | 0.8             | - 0.5 | 0.8             |       |

| Input High Voltage     | V <sub>IH</sub>   |                                                      | 2.0   | V <sub>cc</sub> | 2.0   | V <sub>cc</sub> | V     |

| Output Low Voltage     | V <sub>OL</sub>   | I <sub>OL</sub> = 3.2mA                              |       | 0.4             |       | 0.4             |       |

| Output High Voltage    | V <sub>OH</sub>   | I <sub>OH</sub> = -1mA                               | 2.4   | v <sub>cc</sub> | 2.4   | V <sub>cc</sub> |       |

### CAPACITANCE

| PARAMETER                | SYMBOL           | TEST CONDITIONS       | MAX | UNITS |  |

|--------------------------|------------------|-----------------------|-----|-------|--|

| Input/Output Capacitance | C <sub>I/O</sub> | V <sub>I/O</sub> = 0V | 5   | 25    |  |

| Input Capacitance        | Cin              | V <sub>IN</sub> = 0V  | 5   | p⊦    |  |

NOTE: These parameters are periodically sampled, not 100% tested.

#### **DEVICE OPERATION**

When  $\overline{W}$  is high, the data input buffers are inhibited to prevent erroneous data from getting into the array. As long as  $\overline{W}$  remains high, the data stored cannot be changed by the addresses Chip Select, or data I/O voltage levels and timing transitions. The block diagram also shows data storage cannot be changed by  $\overline{W}$ , the addresses, or the input data as long as  $\overline{S}$  is high. Either  $\overline{S}$  or  $\overline{W}$  by itself, or in conjunction with the other, can prevent the extraneous writing due to signal transitions.

A read occurs during the overlap of  $\overline{S}$  low and  $\overline{W}$  high.

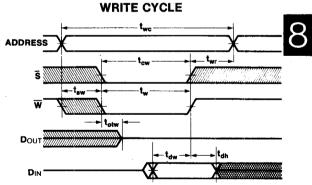

Data within the array can only be changed during a Write time, defined as the overlap of  $\overline{S}$  low and  $\overline{W}$  low. To prevent the loss of data, the addresses must to properly established during the entire Write time plus  $t_{wr}$ .

## **AC CHARACTERISTICS**

TEST CONDITIONS:  $V_{CC} = +5V \pm 5\%$ ,  $T_A = 0$ °C to +70°C  $t_f = t_f = 10$ ns,  $V_{IL} = 0.8V$ ,  $V_{IH} = 2.0V$ , Output Load = 1 TTL Gate and 100pF Input and Output Timing Reference Level = 1.5V

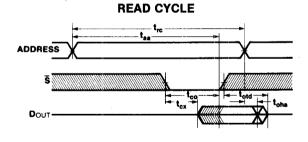

#### **READ CYCLE**

|                                  | SYMBOL           | 2114-2<br>2114L2 |     | 2114-3<br>2114L3 |     | 2114<br>21114L |     |       |

|----------------------------------|------------------|------------------|-----|------------------|-----|----------------|-----|-------|

| PARAMETER                        |                  | MIN              | MAX | MIN              | MAX | MIN            | MAX | UNITS |

| Read Cycle Time                  | t <sub>rc</sub>  | 200              |     | 300              |     | 450            |     |       |

| Access Time                      | t <sub>aa</sub>  |                  | 200 |                  | 300 |                | 450 |       |

| S to Output Valid                | t <sub>co</sub>  |                  | 70  |                  | 100 |                | 100 | l ns  |

| S to Output Active               | t <sub>cx</sub>  | 20               |     | 20               |     | 20             |     | "     |

| Output Three-State from Deselect | t <sub>otd</sub> | 0                | 50  | 0                | 80  | 0              | 100 | ]     |

| Output Hold from Address Change  | t <sub>oha</sub> | 50               |     | 50               |     | 50             |     | ]     |

#### WRITE CYCLE

|                               | SYMBOL           | 2114-2<br>2114L2 |     | 2114-3<br>2114L3 |     | 2114<br>2114L |     |       |

|-------------------------------|------------------|------------------|-----|------------------|-----|---------------|-----|-------|

| PARAMETER                     |                  | MIN              | MAX | MIN              | MAX | MIN           | MAX | UNITS |

| Write Cycle Time              | t <sub>wc</sub>  | 20Ò              |     | 300              |     | 450           |     |       |

| Write Time                    | t <sub>w</sub>   | 120              |     | 150              |     | 200           |     | 1     |

| Write Release Time            | t <sub>wr</sub>  | 0                |     | 0                |     | 0             |     | 1     |

| Output Three-State from Write | t <sub>otw</sub> | 0                | 60  | 0                | 80  | 0             | 100 | 1     |

| Data to Write Time Overlap    | t <sub>dw</sub>  | 120              |     | 150              |     | 200           |     | ns    |

| Data Hold from Write Time     | t <sub>dh</sub>  | 0                |     | 0                |     | 0             |     | 1     |

| Address Setup Time            | taw              | 0                |     | 0                |     | 0             |     |       |

| S Select Pulse Width          | t <sub>cw</sub>  | 120              |     | 150              |     | 200           | ,   |       |

## **TIMING DIAGRAMS**

Note:  $\overline{\mathbf{W}}$  is high for a READ cycle.

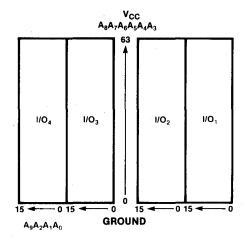

## 2114 BIT MAP DIAGRAM